#### ABSTRACT

#### HAZELWOOD, KIM MICHELLE

#### Dynamic Optimization Infrastructure and Algorithms for IA-64

#### (Under the direction of Dr. Thomas M. Conte)

Dynamic Optimization refers to any program optimization performed after the initial static compile time. While typically not designed as a replacement for static optimization, dynamic optimization is a complementary optimization opportunity that leverages a vast amount of information that is not available until runtime. Dynamic optimization opens the doors for machine and user-specific optimizations without the need for original source code.

This thesis includes three contributions to the field of dynamic optimization. The first main goal is the survey of several current approaches to dynamic optimization, as well as its related topics of dynamic compilation, the postponement of some or all of compilation until runtime, and dynamic translation, the translation of an executable from one instruction-set architecture (ISA) to another.

The second major goal of this thesis is the proposal of a new infrastructure for dynamic optimization in EPIC architectures. Several salient features of the EPIC ISA prove it to be not only a good candidate for dynamic optimization, but such optimizations are essential for scalability that is up to par with superscalar processors. By extending many of the existing approaches to dynamic optimization to allow for offline optimization, a new dynamic optimization system is proposed for EPIC architectures. For compatibility reasons, this new system is almost entirely a software-based solution, yet it utilizes the hardware-based profiling counters planned for future EPIC processors.

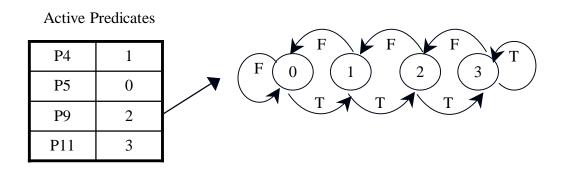

Finally, the third contribution of this thesis is the introduction of several original optimization algorithms, which are specifically designed for implementation in a dynamic optimization infrastructure. Dynamic if-conversion is a lightweight runtime algorithm that converts control dependencies to data dependencies and vice versa at runtime, based on branch misprediction rates, that achieves a speedup of up to 17% for the SpecInt95 benchmarks. Several other algorithms, such as predicate profiling, predicate promotion and false predicate path collapse are designed to aid in offline instruction rescheduling.

# DYNAMIC OPTIMIZATION INFRASTRUCTURE AND ALGORITHMS FOR IA-64

by

# KIM MICHELLE HAZELWOOD

A thesis submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Master of Science

### **COMPUTER ENGINEERING**

Raleigh

2000

**APPROVED BY:**

Dr. Thomas M. Conte, Chair of Advisory Committee

**Dr. Eric Rotenberg**

Dr. Injong Rhee

#### BIOGRAPHY

Kim Hazelwood was born on July 23, 1976 in Richmond, Virginia and grew up in Melbourne, Florida. She graduated first in her class with a Bachelor of Science degree in Computer Engineering from Clemson University in August 1998. During her years as an undergraduate, she participated in the cooperative education program working with Kemet Electronics Corporation in Greenville, South Carolina. She also participated in the Calhoun College Honors Program at Clemson University, as well as the Summer Undergraduate Research Program sponsored by the National Science Foundation where she worked in the Parallel Architecture Research Laboratory.

She then went on to the master's program at North Carolina State University working under the direction of Professor Thomas M. Conte. While working toward her master's degree, Kim spent a summer interning with the CarbonFIRE Dynamic Optimization group at Hewlett-Packard Company in Cupertino, California, and a summer with the Dynamo group at Hewlett-Packard Laboratories in Cambridge, Massachusetts.

She plans to continue her graduate education working toward her Ph.D. in Computer Engineering.

| LIST OF TA                      | ABLES                                                                                                                                                              | V                                |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LIST OF FIG                     | GURES                                                                                                                                                              | vi                               |

| Chapter 1                       | Introduction                                                                                                                                                       | 1                                |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Motivation for Dynamic Optimization<br>Current Approaches<br>Dynamic Compilation vs. Optimization<br>Dynamic Translation vs. Optimization<br>Layout of the Thesis. | 6<br>7<br>8                      |

| Chapter 2                       | Background                                                                                                                                                         | 11                               |

| 2.1                             | Dynamic Optimization Efforts2.1.1Dynamo – HP Labs2.1.2Morph2.1.3Evolutionary Compilation                                                                           | 11<br>15                         |

| 2.2                             | Dynamic Compilation Efforts2.2.1DyC2.2.2DCG2.2.3Dynamo – Indiana University2.2.4Runtime Optimization2.2.5Tempo2.2.6Summary                                         | 20<br>21<br>23<br>24<br>26<br>29 |

| 2.3                             | Translation and Emulation Efforts.2.3.1DAISY2.3.2Crusoe2.3.3FX!32                                                                                                  |                                  |

| 2.4                             | <ul> <li>Profiling Monitors For Feedback-Directed Optimization</li></ul>                                                                                           | 35<br>36<br>38<br>39<br>40       |

| 2.5                             | Useful Tools for Dynamic Optimization<br>2.5.1 DynInstAPI<br>2.5.2 EEL<br>2.5.3 OM                                                                                 | 42<br>42<br>43                   |

| Chapter 3                       | Salient Features of EPIC Architectures                                                                                                                             | 45                               |

| 3.1                             | New Features of IA-64                                                                                                                                              | 45                               |

# TABLE OF CONTENTS

| 3.2       | Summary                                                   | 53 |

|-----------|-----------------------------------------------------------|----|

| Chapter 4 | DO: A Dynamic Optimization Infrastructure                 | 54 |

| 4.1       | An Extension of Dynamo                                    | 56 |

| 4.2       | Performance Improvements Achieved by HPL's Dynamo         | 57 |

| 4.3       | A High-Level Description                                  | 60 |

| Chapter 5 | Dynamic Optimization Opportunities and Algorithms         | 65 |

| 5.1       | Sampling Study: Branch Mispredictions                     | 65 |

|           | 5.1.1 Misprediction Sampling Based on First N Occurrences | 66 |

|           | 5.1.2 Adaptive Warmup Exclusion                           | 68 |

| 5.2       | New Dynamic Optimization Algorithms                       | 71 |

|           | 5.2.1 Dynamic If-Conversion                               | 74 |

|           | 5.2.2 Dynamic Reverse If-Conversion                       |    |

|           | 5.2.3 Dynamic Rescheduling for Scalability                |    |

|           | 5.2.4 Predicate Promotion with Double Predication         |    |

|           | 5.2.5 False Predicate Path Collapse                       |    |

|           | 5.2.6 Predicate Profiling and Prediction                  |    |

|           | 5.2.7 Dynamic Instruction Hint Adjustment                 |    |

| Chapter 6 | Conclusions & Future Work                                 | 92 |

| Chapter 7 | Bibliography                                              | 96 |

# LIST OF TABLES

| Table 2.1 – Summary of Past Approaches          | 31 |

|-------------------------------------------------|----|

| Table 3.1 – The Six IA-64 Instruction Types     | 47 |

| Table 3.2 – Possible Instruction Combinations   | 47 |

| Table 5.1 – IA-64 Branch Instruction Completers | 91 |

# LIST OF FIGURES

| Figure 2.1 – How HPL's Dynamo Works [6]12                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 – The Harvard University Morph Project [46]16                                                                                                           |

| Figure 2.3 – Sathaye's Evolutionary Compilation System [40]19                                                                                                      |

| Figure 2.4 – UW's DyC Dynamic Compilation System [18]22                                                                                                            |

| Figure 2.5 – Kistler's Dynamic Runtime Optimization System [27]27                                                                                                  |

| Figure 2.6 – Illinois' Monitor Table Hardware for Hot-Spot Detection [37]                                                                                          |

| Figure 2.7 – The Profile Buffer Hardware [9]40                                                                                                                     |

| Figure 2.8 – Runtime Code Insertion via DynInstAPI43                                                                                                               |

| Figure 3.1 – An IA-64 Instruction Bundle47                                                                                                                         |

| Figure 3.2 – An IA-64 Instruction Sequence Without Control Speculative Loads                                                                                       |

| Figure 3.3 – An IA-64 Instruction Sequence With Control Speculative Loads                                                                                          |

| Figure 3.4 – An IA-64 Instruction Sequence Without Data Speculative Loads50                                                                                        |

| Figure 3.5 – An IA-64 Instruction Sequence Utilizing Data Speculative Loads50                                                                                      |

| Figure 3.6 – Sample C Code With Branches                                                                                                                           |

| Figure 3.7 – Corresponding IA-64 Predicated Instructions                                                                                                           |

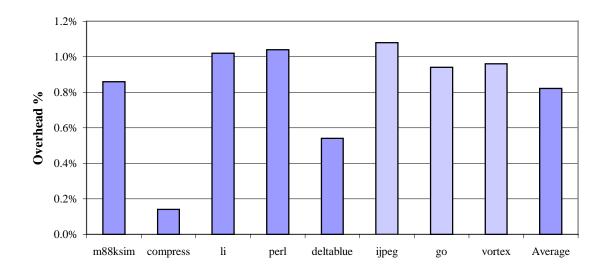

| Figure 4.1 – Dynamo Overhead as a Percentage of Execution Time                                                                                                     |

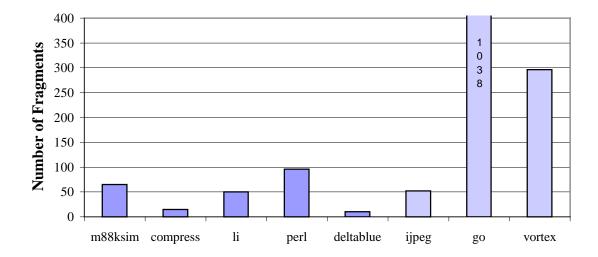

| Figure 4.2 – The Smallest Number of Fragments that Account for 90% of the Total<br>Execution Time                                                                  |

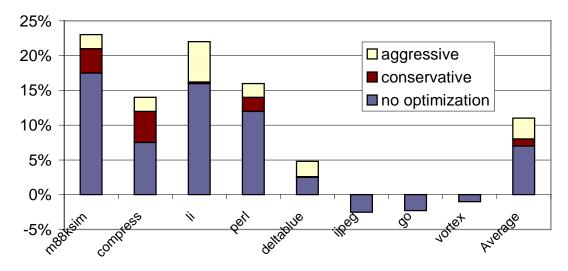

| Figure 4.3 – Wall Clock Time Comparison of Dynamo Performance to Native Execution                                                                                  |

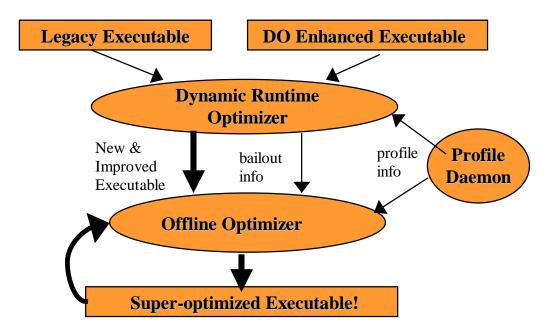

| Figure 4.4 – The DO Dynamic Optimization Infrastructure                                                                                                            |

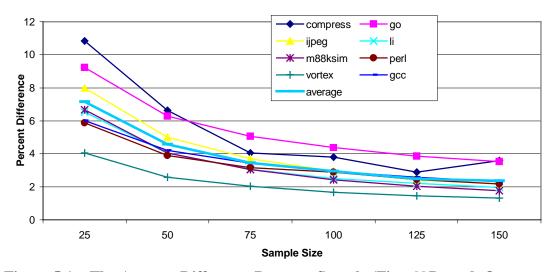

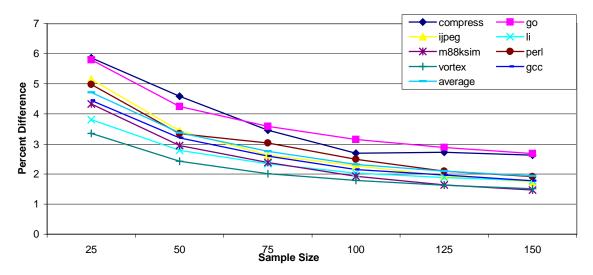

| Figure 5.1 – The Average Difference Between Sample (First <i>N</i> Branch Occurrences) and Actual Misprediction Rates for all Branches in the SPECint95 Benchmarks |

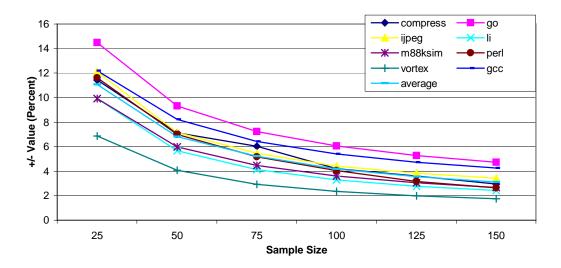

| Figure 5.2 – Error Values for 99% Confidence Interval                                                                                                              |

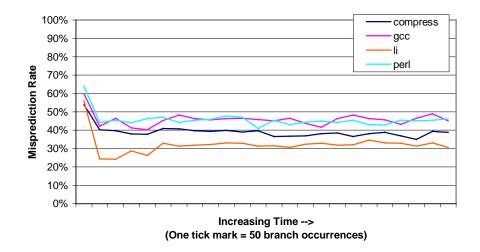

| Figure 5.3 – Misprediction Rate Over Time for Certain Hard-to-Predict Branches in SPECint95                                            | .69 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

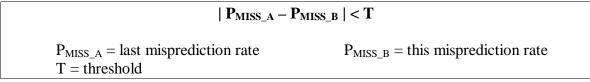

| Figure 5.4 – Determining the End-of-Warmup Condition                                                                                   | .70 |

| Figure 5.5 – Mean Difference Between Sample (First <i>N</i> Branch Occurrences Ignoring Warm-up Period) and Actual Misprediction Rates | .70 |

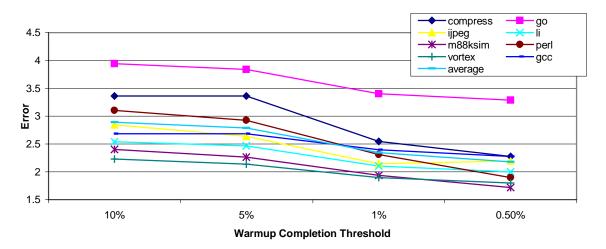

| Figure 5.6 – Effect of Varying the Warm-up Completion Threshold Value                                                                  | .70 |

| Figure 5.7 – If-Conversion Example                                                                                                     | .75 |

| Figure 5.8 – A Predication Algorithm                                                                                                   | .77 |

| Figure 5.9 – A General Predication Algorithm                                                                                           | .77 |

| Figure 5.10 – Dynamic If-Conversion Algorithm                                                                                          | .78 |

| Figure 5.11 – Maximum Allowable Branch Distance                                                                                        | .79 |

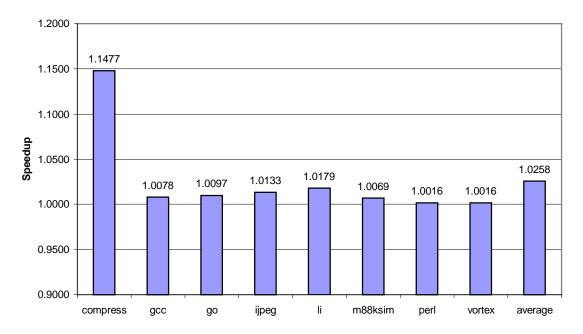

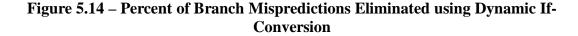

| Figure 5.12 – Speedup from Applying the Dynamic If-Conversion Algorithm                                                                | 80  |

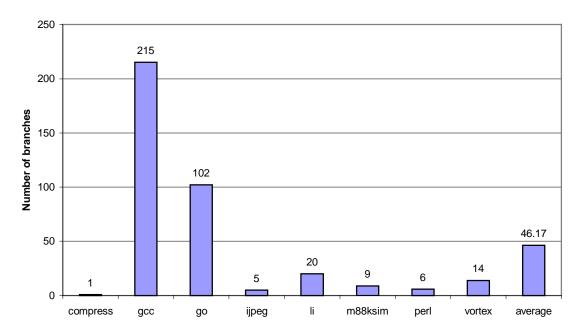

| Figure 5.13 – Number of Branches Converted to Predicates                                                                               | .80 |

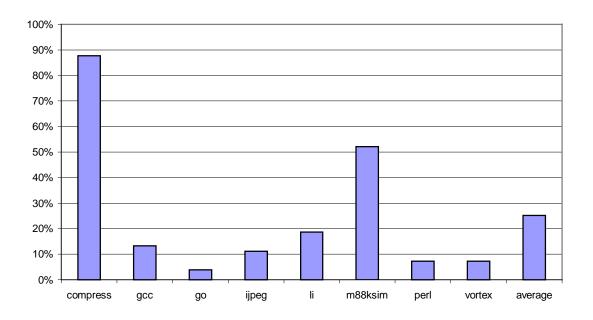

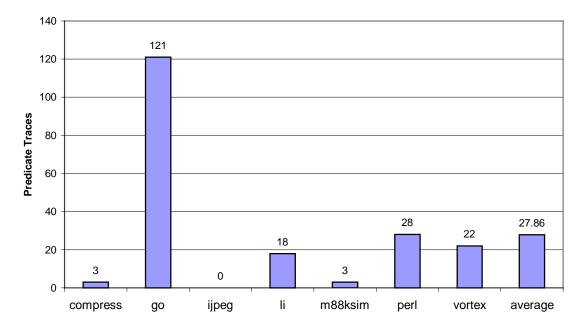

| Figure 5.14 – Percent of Branch Mispredictions Eliminated using Dynamic If-Conversio                                                   |     |

| Figure 5.15 – The Dynamic Reverse If-Conversion Algorithm                                                                              | .82 |

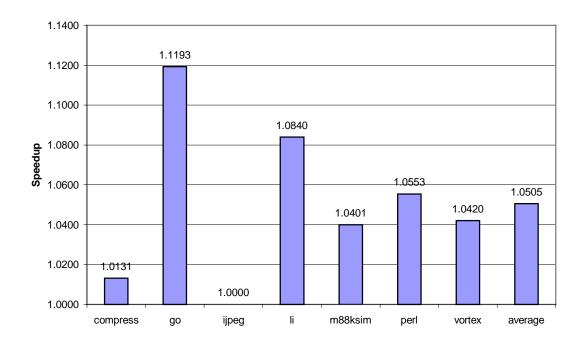

| Figure 5.16 – Speedup Resulting from Dynamic Reverse-If-Conversion                                                                     | 83  |

| Figure 5.17 – Actual Number of Predicate Traces Converted to Branches                                                                  | .84 |

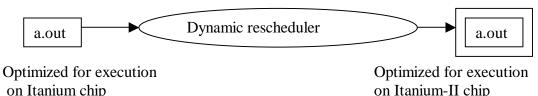

| Figure 5.18 – Dynamic Rescheduling                                                                                                     | .86 |

| Figure 5.19 – IA-64 Instructions With an Instruction Group Boundary                                                                    | 87  |

| Figure 5.20 – Breaking the IA-64 Instruction Group Boundary                                                                            | .87 |

| Figure 5.21 – An Example of False Predicate Path Collapse                                                                              | .88 |

| Figure 5.22 – Predicate Profiling Mechanism                                                                                            | .89 |

# Chapter 1 Introduction

When inspecting the basic run-time performance equation, runtime = instruction count \* cycles per instruction \* cycle time [22], it becomes clear that a reduction in the overall runtime of a program can be accomplished by reducing any of the three variables – instruction count, cycles per instruction, or cycle time. The ideas discussed in this thesis attempt to reduce the run time of a given program by reducing both its instruction count and its cycles per instruction. This run-time reduction is not the result of new compiler techniques, as is typically the case. A dynamic optimization system is presented, which supplements the optimization performed by the static compiler and allows for a uniform level of optimization for all executables.

*Dynamic Optimization* refers to any optimization of software that is performed after the initial compile. Dynamic optimizations can be performed as the program is running or anytime thereafter, such as during the exit procedure of a program of even after the program has exited – during the idle time of the computer. Dynamic optimization can be used to leverage a large set of run-time information that is not available to the static compiler. This information can range from run-time constants to operator usage patterns. Such information can provide the foundation for an entirely new set of optimization algorithms.

Dynamic optimization is especially challenging due to the strict performance requirements for runtime optimization. Typically, our industry is not willing to accept a new idea unless performance improvements are seen immediately. Therefore, the standard lower-bound for dynamic optimization performance is that it must result in an overall system that performs at least as well as a system that does not employ dynamic optimization. While it is possible that users will permit some program slowdown if it is a one-time occurrence, this is only true in the case that performance of the program is improved to the extent that the average runtime over time is notably improved.

## **1.1** Motivation for Dynamic Optimization

Several factors may lead to the decision to implement a dynamic optimization system. Often, decisions made by a static compiler are not well suited for the runtime behavior of the program. This may be due a variance in the usage patterns of the client, a change or upgrade of hardware (such as the pipeline structure) since the initial compile time, or simply an overly aggressive static compilation decision. The current software development cycle does not provide an opportunity for correcting or changing decisions made by the static compiler. Dynamic optimization can provide this flexibility in the software development cycle.

The limitations of a static-only optimization scheme make dynamic optimization an appealing option. Runtime values and branch behavior are known and can be leveraged in an effective manner. Some of the most prominent observations that led up to the need for dynamic optimization are described in the next subsections.

*Software Vendor Optimization Levels.* One justification for a dynamic optimization system concerns the large amounts of off-the-shelf software packages that are purchased every year. Ideally, all software vendors would employ the highest level of optimization during their compilation process. Yet this is often not the case. Vendors may forgo high optimization levels because of the compile time necessary or because of

the difficulty of debugging an executable with a high level of optimization. The varying level of compile technology available in the compilers used by software vendors has resulted in an unknown level of optimization in off-the-shelf software products and consumers have no way of ensuring that high levels of optimization were employed in the products they purchase. Dynamic optimization allows even the latest advances in optimization technology to be introduced to existing software, therefore ensuring optimal performance. For instance, Hewlett-Packard Laboratories has shown that programs originally compiled with level-2 optimization (-O2) running under their Dynamo dynamic optimization system performs as well as the same program compiled with level-4 optimization (-O4) without dynamic optimization [6].

*Processor Changes Within an ISA.* Yet another reason for choosing to implement dynamic optimization concerns processor upgrades within a processor family and cross-generation compatibility between processor families [10], [14], [40]. A program compiled for a given instruction-set architecture (ISA) can be run on any processor implementing that ISA. The program is only optimized, however, for execution on a processor with an identical execution pipeline, identical function units, and identical instruction availability. Variances in any of these attributes result in a program that is not employing the available functionality of the processor. Even worse, incorrect execution is possible for processors that do not check instruction dependencies at runtime, such as traditional VLIW processors or RISC processors that have load-use delay slots.

Allowing a user to recompile for his/her own system could easily provide for custom optimization, yet in the current software development cycle a recompilation requires original source code. Clearly, software vendors would not want to release their source code due to the proprietary information available within. Releasing versions of the executable for every single processor would furthermore be quite tedious. Dynamic optimization enables custom optimization for any processor within an ISA from a single executable, without the need for original source code.

*Changes in Usage Patterns.* Ideally, a program should be optimized based on how it is used. Unfortunately, usage patterns vary from person to person, and even one person's usage may vary over time [40] as they discover new features of the software. Since conventional compilation optimizes the program only once and before the user runs the program, optimization will either (1) *not* take into account actual user behavior, or (2) base optimization on an average profile. There is no guarantee that the average profile information is at all representative of typical user behavior. Representative profile information is difficult to produce because of the large variance among users, and over time for the same user. This sheds doubt on the effectiveness of a unified set of profile data.

Dynamic optimization allows for software that is optimized for the particular user. Code can be optimized to better represent actual runtime behavior for each and every run of a program. It allows for continued optimization as the client's usage patterns change. This level of customization is simply not possible with conventional static optimization methods.

*Trend Toward Static Scheduling.* While most of the processors of the past rely on dynamic scheduling of instructions, an upcoming generation of processors contains a simpler processor core that relies on static scheduling. Scheduling programs once, and

even before the program executes, increases the importance of accurate profile data. Inaccurate profiles result in poor scheduling decisions that will affect every run of a program [40]. Because static scheduling involves a great deal of speculation, poor scheduling choices can greatly harm runtime performance. At this time, unfortunately, there is no widely accepted and used means for correcting poor scheduling choices by the static scheduler. Dynamic optimization, on the other hand, may be effectively used to leverage runtime information in order to recognize poor static scheduling choices and correct them.

*Power Reduction.* A well-designed dynamic optimization system has great potential for venturing into other domains, such as power reduction. There are many opportunities for noting the runtime power consumption and making changes that focus on consuming less power. For example, code transformations can be performed that result in less bit flips between sequences of instructions [43]. Reduced bit flips result in reduced power consumption. Rather than having a NOP instruction equate to adding two zeros together, it could add the inputs of the previous instruction while storing the result in a free register. As processors become more and more power hungry, dynamic optimization could become an essential tool for balancing power and performance in a case-by-case basis.

*Complementary Optimization Opportunity.* There is an abundance of information unavailable at static compile time that can be leveraged by dynamic optimizations. Optimizations can be based on run-time constants and may span library and function calls. Branch behavior for the particular run is known, so more aggressive optimizations can be performed. But most notable is the fact that dynamic optimization

can be completely compatible with the array of static optimizations already implemented in conventional compilers.

# **1.2** Current Approaches

There are various approaches to dynamic optimization. One approach is direct optimization of the binary executable using an executable editing mechanism. This method is typically system dependent, yet it results in a dynamic optimization infrastructure that does not have any front-end compiler requirements - any existing executable can be optimized requiring no special compilers or programming languages. Another approach involves performing optimizations on intermediate representations of the program, which are generated at the same time as the executable itself. This approach simplifies the optimization procedure and provides for system independency, yet it requires all software vendors to produce intermediate representations of their software. Intermediate representations, which can typically be reverse engineered to produce original source code, are not popular among software vendors. A variation of that approach, however, is the generation of an intermediate representation from the final executable, upon which optimizations are performed. This approach, while not as fast as the direct optimization of the original executable, provides for system-independent optimizations.

Dynamically optimized code can either be immediately consumed, it may be cached for use during the current or subsequent executions, or it may be permanently applied to the executable. It is evident that any optimizations that are based on the propagation of runtime constants cannot be permanently applied to the executable, as

6

they would not be correct in subsequent runs. Yet there are several optimizations that can be permanently applied, such as rescheduling based on a hardware change.

The time at which optimizations are performed is another design decision. Most of the current research efforts focus on one of the following optimization opportunities:

- compile time, i.e. static optimization [36]

- run time, i.e. on-line dynamic optimization [6], [8], [10], [14], [27], [28]

- idle time, i.e. off-line dynamic optimization [27], [46]

All dynamic optimizations can be classified as either heavyweight or lightweight optimizations. Heavyweight optimizations make the largest amount of impact on program performance. Not surprisingly, heavyweight optimizations take the largest amount of time to perform, and therefore may not always be feasible to perform at runtime. They can, however, be performed offline, during the idle time of the computer. Lightweight optimizations, on the other hand, can typically be performed at runtime. Again, not surprisingly, most lightweight optimizations do not result in the same level of performance improvement as that of heavyweight optimizations.

The advantages and disadvantages of each of the current approaches for performing dynamic optimization will be explored in detail in Chapter 2, the background section.

## **1.3** Dynamic Compilation vs. Optimization

Some researchers make a sharp distinction between *dynamic optimization*, the optimization of compiled executables, and *dynamic compilation*, postponing some or all

of static compilation until runtime and therefore invoking compilation on a code format that would not otherwise execute [6], [27].

Dynamic compilation differs from dynamic optimization in their means for optimization. Dynamic compilation is performed on code that was specially designed for the task. Special compilers and programming languages are required in order to generate an executable containing holes (portions of uncompiled code) that will be filled in at runtime. No special compiler or programming language is required for dynamic optimization, however, because all optimizations are performed on a working executable.

Projects involving both dynamic optimization and dynamic compilation are described in the background section, however all of the original ideas presented in this thesis focus exclusively on dynamic optimization.

# **1.4 Dynamic Translation vs. Optimization**

Another distinction must be made between *dynamic optimization* and *dynamic translation* or *emulation* projects. Translation or emulation systems allow an executable compiled for one ISA to execute on a processor featuring another ISA. While translation systems may optimize the code that is translated, the *primary* goal is compatibility.

Several systems falling into the translation/emulation category are discussed in the related-work chapter in order to clarify the difference between these systems and the dynamic optimization system proposed later in this thesis.

### **1.5** Layout of the Thesis

The purpose of this thesis is to explore many old and new approaches for dynamically optimizing executables. This includes the analysis of the goals associated with dynamic optimization and the means for accomplishing the goals. Also presented is an infrastructure for the dynamic optimization of EPIC computers. In addition, several new dynamic optimization algorithms are presented which leverage features of an EPIC architecture.

Chapter 2 of this thesis contains background information. Several research projects involving dynamic optimization are discussed including the potential advantages and disadvantages of each approach. Three projects involving dynamic optimization (Section 2.1), five projects involving dynamic compilation (Section 2.2), and three projects involving dynamic translation (Section 2.3) are included in the discussion. Next, Section 2.4 discusses the current research on profiling monitors for feedback-directed optimizations. Several useful tools are available that can be leveraged in any dynamic optimization project. These tools are discussed in Section 2.5.

Chapter 3 describes the salient features of EPIC architectures and describes why EPIC is a good target for dynamic optimization.

Shortcomings discovered in many of the current research approaches led to the proposal of a new dynamic optimization system. Chapter 4 motivates and presents a high-level view of the DO dynamic optimization system. DO is a combination online/offline dynamic optimizer that is built on the solid foundation already available in the dynamic optimization research community.

One line of study that few researchers have ventured into is the development of specialized runtime optimization algorithms. Chapter 5 introduces a set of new dynamic optimization algorithms designed for implementation in EPIC architectures. After laying the groundwork for dynamic optimizations by studying the optimal time at which the optimizations should be performed, Section 5.2 goes on to introduce several new dynamic optimization algorithms that are specially designed for runtime implementation on EPIC architectures. Finally, Chapter 6 concludes that dynamic optimization is a promising new field and there is much work that can be done as future research.

# Chapter 2 Background

Many research groups are currently working on Dynamic Optimization efforts in one of its many forms. Some groups work exclusively within a given instruction set architecture (ISA), gearing their optimizations toward reoptimizing for differing features of processors within a processor family or user behavior. Others work between ISAs. In this case, the final product does the job of emulating one instruction set on a different instruction-set architecture.

The purpose of the following sections is to provide an overview of some of the similar research efforts that are currently underway. A brief description of each of the approaches is mentioned, along with any notable advantages or disadvantages of the model.

# 2.1 Dynamic Optimization Efforts

About a dozen research groups are currently exploring dynamic optimization, compilation, or emulation techniques. Each group has a different set of approaches for accomplishing the overall goals. The approaches differ in when, how, and what is optimized. Some of the concepts contained within the approaches can be reorganized and balanced to form a new, more universal approach to dynamic optimization.

#### 2.1.1 Dynamo – HP Labs

A group of researchers at Hewlett-Packard Laboratories developed a dynamic optimization system, which they call Dynamo. Dynamo is a caching and linking

mechanism that works to optimize native executables and DLLs (dynamically-linked libraries) at run time [6].

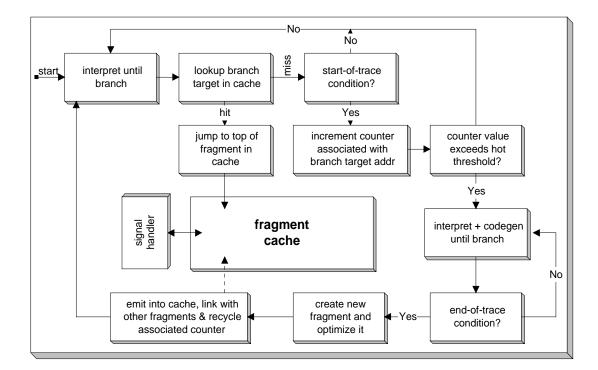

Figure 2.1 – How HPL's Dynamo Works [6]

Figure 2.1 [6] shows how Dynamo selects, optimizes and stores program fragments. As indicated in the figure, Dynamo interprets a native binary until it detects a hot trace. This is determined by observing the branches in the program. If that branch target meets certain conditions, such as being the target of a backward-taken branch, a counter associated with the target address is incremented. Only when the counter exceeds a certain threshold value is the trace deemed a hot trace (in the case of Dynamo, the threshold is 50.) The corresponding program fragment (an executable unit of trace instructions) is inserted into the software-based code cache, using a very speculative but simple trace-selection scheme. It is assumed that the path immediately following a hot

entry point is likely to be taken in the future. Link stubs are inserted to catch any offtrace branches, in order to direct execution to the correct location, which may also be in the code cache. From that point forward, anytime the particular branch target address is encountered, Dynamo takes control and executes the optimized instructions from the fragment cache.

Dynamo ensures that time is not wasted optimizing infrequently executed fragments; only *hot* fragments are selected for optimization. This method of determining hot traces ensures that Dynamo doesn't waste time dealing with infrequently executed code. If effort were spent optimizing every program fragment, the interpretation overhead of Dynamo would be unacceptable.

HP Labs' Dynamo group points out an important distinction between their work and the solutions that are currently being developed by other research groups. First, they assume that the starting point for optimization is a native program binary. For this reason, no translation step is involved. This significantly reduces the complexity of the Dynamo solution, while allowing it to be effectively used with any existing executable. Second, the Dynamo group points out the difference in their solution and the solutions that involve *dynamic compilation*. Dynamo does not postpone any part of the compilation process until runtime. This design decision was made because the group felt that the solution should be transparent. Dynamic compilation solutions require a set of program annotations that must be inserted by the programmer, or they require the use of a new programming language that has been designed for the task of dynamic compilation. Solutions of this sort are less transparent, and are therefore excluded from the Dynamo framework. This design decision is especially notable because it allows the dynamic optimizer to bail out at any point without any adverse effects within the program itself. Bailout occurs when the amount of time spent in the fragment cache falls below a certain threshold. Dynamo suspends execution and allows the program to run directly on the underlying processor.

Another distinctive feature of Dynamo is that it is completely online, that is, all optimizations are performed at runtime. All data that is generated to aid in optimization is used within the same execution; no data is written out for later optimizations.

Yet the most notable feature of Dynamo is the performance. Even without employing any optimizations, Dynamo's methods produce speedup by storing fragments in the fragment cache. These fragments are executable traces through the code with many of the branches and procedure calls removed. Even many off-trace branches within a particular trace result in hits in the fragment cache. Taken branches normally limit fetch bandwidth, therefore the removal of procedure call and branch overheads for frequently executed paths results in an overall speedup of the code. Optimizations performed on the traces result in even higher levels of speedup.

The major advantage of Dynamo is that it is a binary-to-binary solution. No special compilation methods are needed; therefore the solution is applicable to all future applications, as well as legacy executables. Dynamo is rare in that it is a completely transparent solution. Yet the interpretation feature also requires that custom versions of some of the Dynamo code be written for each processor and operating system.

There is an entire domain of optimization, namely off-line optimization, which Dynamo does not leverage, however. The fact that Dynamo occasionally bails out of certain optimizations, but no information is stored regarding that action, leads to the conclusion that a similar attempt and failure will ensue during each of the subsequent executions. Furthermore, the optimization that was attempted will never be completed, resulting in a suboptimal execution. If information regarding the failed attempt to optimize was maintained in an external file, the dynamic optimizer could avoid the cost of future failed attempts. This external data could also be used in order to complete optimizations off line, such as during any idle time of the operating system.

#### 2.1.2 Morph

Zhang et al, of Harvard University developed a framework for offline dynamic optimization, known as Morph [46]. Unlike Dynamo, which performs all optimizations online (during execution), Morph collects profile information at runtime and uses that information to perform optimizations offline (after the program has exited.)

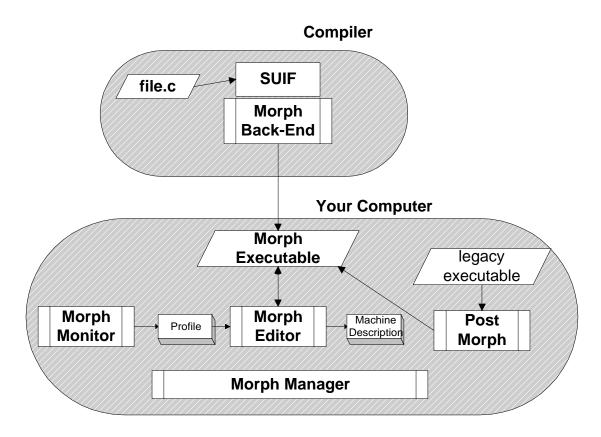

The main components of Morph are the Morph Back-end, the Morph Monitor, the Morph Editor, and the Morph Manager. The Morph Back-end is a portion of the compiler that produces the executable along with shared libraries containing all of the annotations necessary to support dynamic re-optimization. The Morph Monitor is a lowoverhead profiling system that is built into the Digital UNIX operating system and serves the purpose of program monitoring. The Morph Editor is a component built into the SUIF research compiler [20] that performs optimizations on the intermediate representation produced by SUIF and outputs an executable. Finally, the Morph Manager, an off-line system component, makes decisions concerning the time at which to invoke re-optimization of programs based on the data reported by the monitor.

The Morph research group points out three necessary requirements that motivated their design. First, optimizations must occur on the particular machine where the software is actually being executed and should emphasize the usage patterns of the end user. This requirement ensures the effectiveness of profile data. Second, no source code should be required for optimization. This requirement is clearly due to the proprietary nature of industry source code. A dynamic optimization solution that required software vendors to release their source code would not be welcomed by industry. The final requirement is that any optimization performed should be entirely transparent to an end user. A user should be able to benefit from dynamic optimization without any necessary interaction or knowledge of the optimization system. This requirement also encompasses correctness, in that optimization itself must not *break* any working code.

Figure 2.2 – The Harvard University Morph Project [46]

The three requirements listed above show that Morph is geared toward mainstream, industrial use, rather than selective research use. Morph hides complexity and insures that an end user is unaware of the reoptimization being performed, save the performance increase that will be encountered after reoptimization.

A drawback of Morph is that all optimizations are performed after the program has exited. A system such as Morph cannot leverage much of the runtime information that varies from run to run. For example, an optimization such as constant propagation, based on runtime constants, cannot be employed in the optimization process. Furthermore, the profile data collected throughout the course of an execution will be compiled into a single set of averages, and no indication of profile shifting [40] or phased behavior [41] will be evident.

Another concern is the assumption of a single user workstation environment. While Morph may be quite effective at learning the usage patterns of a single user, it could potentially hurt the performance of a multi-user program. It is not designed to be useful in an environment where a centralized binary is shared over a network, as is becoming a more and more common case.

The next drawback of Morph concerns the shared libraries containing program annotation. It is unfortunate that these annotations require compilation with the SUIF research compiler in order to be produced and cannot be generated on the fly. Morph requires a recompilation of all existing software in order to be employed, and cannot be effectively implemented on the large quantities of legacy binaries that are available in industry. While a component of Morph known as Post Morph, which should infer Morph annotations from legacy binaries, has been mentioned briefly, details are scarce. Finally, Morph's program annotation is simply an intermediate representation of the entire program. Maintaining an intermediate representation of an entire program could result in severe code expansion. In addition, software vendors may not be willing to allow an intermediate representation of their software to be maintained on every users system for fear of reverse engineering.

### 2.1.3 Evolutionary Compilation

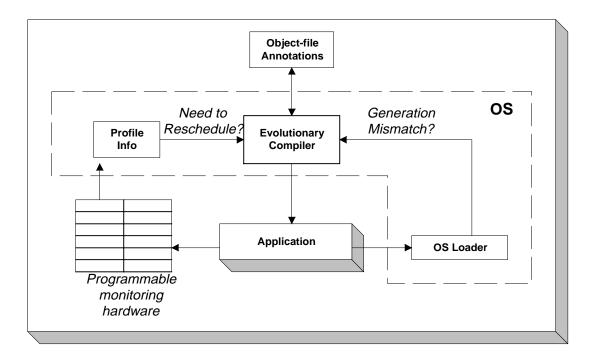

Sumedh Sathaye of North Carolina State University suggested many ideas for an Evolutionary Compilation system in his Ph.D. thesis [40]. His contributions include two schemes for dynamic rescheduling code for VLIW architectures: an evolutionary compiler and a dynamic rescheduler. Sathaye also contributed a technique for reducing dynamic scheduling overhead, known as the Persistent Reschedule-Page Cache (PRC).

Sathaye's evolutionary compilation ideas were based on the notion that the usage patterns of a user evolve over time and that the code must be optimized accordingly. His dynamic rescheduling ideas focused on the different optimization opportunities available between certain processors within a single ISA.

The evolutionary compilation framework is designed to be resident in the operating system and contains a hardware-based program monitor, a loader, and an evolutionary compiler. While the application is executing, the monitoring hardware keeps track of the usage pattern of the application. If it becomes apparent that the usage pattern has changed from that for which the application was optimized, the evolutionary compiler steps in and reschedules the application to better suit the needs of the user.

The OS loader loads an application and determines if there is a generation mismatch between the object code and the machine on which it will be running. If a mismatch exists, the Dynamic Rescheduler steps in at page-fault time and performs object-code transformation with page-sized granularity. This process employs an external file, known as the object-file annotation, which was produced during the initial compile of the application.

Figure 2.3 – Sathaye's Evolutionary Compilation System [40]

Because the process of rescheduling an executable can be time consuming, Sayathe suggested caching the rescheduled versions of the executable in a special PRC, Persistent Rescheduled-Page Cache. This technique reduces scheduling time by storing previously translated code portions and not requiring such portions to be rescheduled and optimized every time they are encountered.

The notable feature of Sayathe's Evolutionary Compilation system is its focus on the profile shift associated with a user's changing usage patterns. While many of the other solutions focused exclusively on optimizing for generation mismatches, Sayathe suggests an alternate optimization stimulus.

A weakness of the system is that all retargeting is performed right at runtime, yet the rescheduled code is not maintained for subsequent executions. While a one-time slowdown for rescheduling might be acceptable, rescheduling during each execution for retargeting to the same processor is unnecessary.

In addition, like the Morph solution, the static compiler generates the program annotations required for rescheduling. This means that only programs compiled using a specialized compiler that generates such annotations can be rescheduled. Evolutionary compilation is not applicable to the volumes of legacy binaries in existence.

Finally, it should be noted that terminology has progressed since Sayathe's use of the phrase *evolutionary compilation*. As stated in the introduction, compilation is a term reserved for the process of generating a native executable from non-native instructions. Today, evolutionary compilation as described by Sayathe is simply referred to as *rescheduling*.

# 2.2 Dynamic Compilation Efforts

Dynamic compilation refers to the postponement of some or all of the static compilation process until runtime. In many cases the static compiler performs some initial compilation activities, but the creation of executable code is not performed until runtime. Dynamic compilation differs from basic dynamic optimization in this respect – the static distributed program is not executable without the dynamic compilation system in place. While dynamic optimization works with files that would otherwise execute, this

is not the case with dynamic compilation. For this reason, there is a strong association between the dynamic compiler and its programs. It would not be easy to switch dynamic compilers if a program was partially compiled with a different dynamic compiler.

Several groups are currently working on projects related to dynamic compilers and dynamic compilation methodologies. Some of the research efforts are discussed in the following subsections.

### 2.2.1 DyC

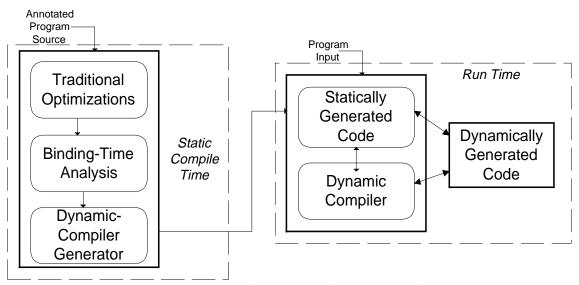

A research group at the University of Washington has developed a rather thorough system to support dynamic compilation called DyC. DyC consists of a declarative annotation language and corresponding compiler [18], [19].

The annotated language resembles C, while including the necessary instructions for providing compiler directives used in dynamic compilation. Differences in the model and a standard programming model are that DyC requires all data to be declared as static or dynamic initially, and requires dynamic compilation possibilities to be explicitly declared by the programmer.

DyC's static compiler produces an executable that contains a combination of statically compiled code and a run-time specializer for the portions of code where dynamic compilation will occur. The run-time specializer allows code to be optimized for various instances of run-time variables. Two control-flow subgraphs, called *setup code* and *template code*, replace each dynamic code region. The setup code contains static computations, while the template code contains dynamic computations. The dynamic template is created containing holes that will be filled in at dynamic compile

time, once the runtime values are known. Scheduling and register allocation is performed on the two subgraphs independently, with no interference between the two.

Finally, custom dynamic compilers are implemented within the code itself, which trigger the dynamic compilation and throw away the corresponding template.

A notable advantage of the DyC model is its speed. The performance can be attributed to its lack of an intermediate format. In addition, no general analysis is performed at run time, as all decisions are made in advance and dynamic compilation is actually coded into the final executable. These two design decisions have led to notable performance gains over other research models.

Figure 2.4 – UW's DyC Dynamic Compilation System [18]

A limitation of DyC that the group plans to improve upon is inadequate support for global variables and partially static data structures [19]. These limitations arise from the fact that each variable and data structure must be initially declared as static or dynamic, and no combinations are permitted. A weakness of the DyC model, however, is that it requires the use of an entirely new language. While the system is a rather complete and adequate environment for dynamic compilation, it cannot be used with existing code. In order for mainstream use to be possible, software developers must switch to the annotated C language.

Should the group decide to automate the annotation process and provide the functionality for DyC to work with standard programming languages, DyC may become a viable option for dynamic optimization in industry.

#### 2.2.2 DCG

DCG, or dynamic code generation, is a system developed by Engler et al. of the Massachusetts Institute of Technology [15]. Dynamic code generation entails the idea of an executable process that creates additional executable code that is tailored to the environment on which the program is run. It is similar to the concept of *self-modifying code*, but rather than altering existing code, the existing code is augmented with additional code.

Within the DCG model, the task of code generation is postponed until run time. Instead, the intermediate representation of the lcc compiler is released, which will be converted to machine code just before execution. Because the intermediate representation is machine-independent, the system is completely retargetable. A single intermediate representation of a program can be used to generate code for any of a number of systems. Furthermore, the resulting executable will be optimized for the architecture on which it was created.

23

A single procedure is the basic unit of code generation within the DCG model. A procedure is compiled by DCG and a pointer to the code is then passed to the client. The code is invoked as an indirect call to a C procedure.

The DCG model takes care of code generation tasks including tree construction and labeling, register allocation, instruction selection, jump resolution, and binary code emission. Not included in the list of tasks is code optimization. While executable code is dynamically generated, DCG makes no efforts to support automatic global optimization or pipeline scheduling. This matter is instead "the responsibility of the client, which has access to the low-level IR specification" [15]. Despite this fact, DCG reserves eight registers for its personal use. The user can utilize these registers for a limited amount of register re-allocation, if desired.

DCG has been shown to be an efficient means for emitting code locally, however it makes no claims, nor any attempts to optimize the code it produces. The limiting factor is the fact that it produces code procedure-by-procedure, and therefore has no global awareness of optimization opportunities. This fact, combined with the fact that optimization issues are left to the client, is a clear weakness of the DCG model in the dynamic optimization domain.

## 2.2.3 Dynamo – Indiana University

Leone et al. of Indiana University have proposed a staged-compiler architecture for dynamic optimization which they also call Dynamo<sup>1</sup> [33].

Within the scheme of Dynamo, the programmer annotates a particular program with directives that specify the conditions under which dynamic optimizations should occur for a certain portion of code and the actions that should be performed in order to optimize the code.

The key feature of Indiana's Dynamo project is the staged compiler concept. During static compilation, only portions of the code that will not benefit from dynamic optimization are compiled into native code. The other portions of code are segmented into lightweight optimization candidates and heavyweight optimization candidates. Lightweight optimizations require little time to perform and only provide minor improvements to code. Heavyweight optimizations, on the other hand, are rather time consuming but typically provide substantial benefits to performance. During static compile time, heavyweight candidates are partially compiled into a high-level intermediate format. This high-level IR is suitable for more aggressive optimizations. Conversely, lightweight candidates are compiled into a mid-to-low-level IR, which is more suitable for simple optimization techniques.

A minimal amount of optimization is performed at static compile time. Selective dynamic optimization is then performed at runtime. The dynamic optimizer begins by performing candidate selection and cost- benefit analysis. Candidate selection allows the system to identify code portions that may benefit from dynamic optimization using a profiler. Cost-benefit analysis then assesses the feasibility of run-time optimization.

The most evident flaw concerns the cost-benefit analyzer. For Dynamo, this step is performed at run time. This form of analysis will most likely be extremely timeconsuming and inaccurate. Not only must it accurately predict the benefit of and time required to perform a particular optimization, it must do so quickly enough not to impact the performance of the executing program. By using critical execution time, analysis of

<sup>&</sup>lt;sup>1</sup> To be fair, the Dynamo project at Indiana University was actually started prior to HPL's Dynamo.

this form actually reduces the amount of dynamic optimization that can be performed at runtime.

Another drawback of IU's Dynamo is many static optimizations are forgone if it appears that they will impact the amount of runtime optimization that will be available. While many other approaches look at dynamic optimization as a complementary optimization opportunity, Dynamo sees it as a replacement for many of the static optimization opportunities.

The Dynamo approach is extremely limited in that it does not perform automatic optimization selection and instead relies on the programmer to recognize optimization opportunities and annotate the code accordingly. Furthermore, in order for existing code to benefit from the Dynamo strategy, the code must be explicitly altered. This attribute alone is such a severe limitation that it can be seen as an indication of why Dynamo may not be viewed as a universal dynamic optimization solution.

#### 2.2.4 **Runtime Optimization**

In an effort labeled Dynamic Runtime Optimization, Kistler, et al. of the University of California at Irvine suggests moving all program optimization to runtime [27]. At compile time, he suggests that the role of the compiler should be to produce an object file that contains a generic tree-based intermediate representation of the program, rather than native machine instructions. No optimizations are performed on the intermediate format, as that would jeopardize its portability. This would allow the intermediate format to be issued to any of a number of processors, which would then optimize the object file to take advantage of the particular features of the processor itself.

This optimization would all be done at runtime, however, utilizing the idle time of the program.

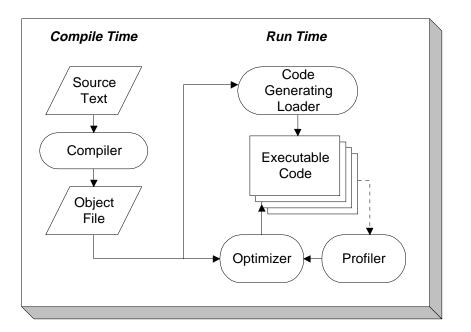

Kistler suggests a new system architecture that consists of four key elements: a compiler, a dynamic code-generating loader, an adaptive profiler, and a dynamic optimizer.

Figure 2.5 – Kistler's Dynamic Runtime Optimization System [27]

The role of the compiler is to generate an intermediate representation object file from the original source code. It is not the role of the compiler, however, to perform any static optimizations, as that may obstruct the opportunity for dynamic runtime optimizations.

The dynamic code-generating loader then transforms the intermediate representation into native machine code at load time, then executes the given code.

During the execution period, the adaptive profiler observes the runtime behavior and gathers all of the necessary information required for future dynamic optimization decisions.

Finally, the dynamic optimizer periodically optimizes code portions that are executed most frequently. The intermediate code representation is optimized in the background during the idle time of the operating system.

One of the major advantages of this runtime optimization model is that it allows the dynamic optimizer to be aware of the time-consuming portions of the code (via the profiler) and to focus optimization efforts on such portions. This is clearly superior to the static optimization model, which applies optimizations uniformly to all code portions, regardless of usage patterns.

The major disadvantage of this system architecture is that a great deal of strain is put on the runtime system. In typical systems, the only task performed at runtime is the execution of native code on the processor. In this system, however, the runtime system takes on the added responsibility of code generation, profiling, and dynamic optimization. Moving this much functionality to the runtime system may not result in the desired performance gains.

In addition, this model increases code size significantly due to the intermediate representation of the code that must be kept around for use in the dynamic optimizer.

This form of runtime optimization is not applicable to the existing code base. It would require software vendors to either release their source code (not an option), or compile their software into the proprietary intermediate format. Furthermore, software vendors may be leery of the intermediate representation of their code that will be kept around. If there is any possibility of decompilation of the IR, vendors will not be willing to implement the optimizer for fear of code piracy. Unfortunately, this model requires 100% compliance by software vendors in order to be effective.

### 2.2.5 Tempo

In 1995, Charles Consel of the University of Rennes / Irisa, France introduced an infrastructure, which he called Tempo, upon which much of the DyC project of the University of Washington was based [11].

Consel was the first to automate the process of run-time specialization, where a template is produced containing holes that correspond to each of the values that are constant at run time. Using formal methods, Consel proved the correctness of his proposed techniques for a variety of languages and developed Tempo, a prototype version of his run-time specializer based in the C programming language.

At compile time, a tree grammar is produced, which is an approximation of the possible program specializations. This tree grammar is produced using programmer annotations in the code that specify the program invariants. The tree grammar is then converted into a set of templates. At run time, a run-time specializer selects the appropriate templates, computes invariants and fills them into the template holes, and relocates jump targets.

This method for dealing with constants known at runtime was revolutionary for its time. When compared to other pre-1995 run-time specializers, Tempo possessed the following notable traits. It was the first automated specializer of its time. While other research groups had employed methods similar to templatizing code, all such templates were created by hand and therefore suffered from the risk of programmer error. Because the Tempo compiler produced the templates automatically, the risk of error was greatly reduced. Second, Tempo's correctness was formally proven and published [11]. Third, although a prototype was developed in C, the details of Tempo were applicable to any of a number of programming languages. Fourth, this model was the first of its kind to be portable. And finally, Tempo was shown to be an efficient means of run-time specialization. The code produced required as little as three runs to amortize the cost of specialization, resulting in code that ran five times faster.

On the negative side, Tempo addressed only one of the numerous goals of dynamic optimization. Tempo makes no attempt to deal with issues such as rescheduling code for differing architectures, or register reallocation.

Furthermore, the one goal that Tempo did address, it did so in a manner that required a great deal of programmer effort. While the task of template creation was in fact automated, the task of determining potential templatized portions was still the duty of the programmer. This not only required effort and knowledge on behalf of the programmer, but it introduced the potential for error and/or suboptimal specialization.

### 2.2.6 Summary

The dynamic compilation and optimization methods presented in this section can be summarized in Table 2.1. Several of the research groups employed dynamic compilation, which is an interesting approach but it requires a great deal of software development effort. New compilers and programming languages are required in order to employ such an approach. Other groups chose the dynamic optimization route, however approaches varied widely. The approaches ranged from a high amount of user effort required, to completely transparent approaches that required no user effort at all. Most approaches perform optimizations at runtime and very few perform any optimizations offline.

| Name      | Dynamic      | Dynamic     | At      | After   | User   | Comments        |

|-----------|--------------|-------------|---------|---------|--------|-----------------|

|           | Optimization | Compilation | Runtime | Runtime | Effort |                 |

| DyC       |              | X           | Х       |         | High   |                 |

| Morph     | X            |             |         | Х       | Med    |                 |

| Dynamo-   | Х            |             | Х       |         | Lo     |                 |

| HP Labs   |              |             |         |         |        |                 |

| Dynamo-   |              | Х           |         |         | High   |                 |

| Indiana U |              |             |         |         |        |                 |

| DCG       |              | Х           | Х       |         | High   | No Optimization |

| EC        | Х            |             | Х       |         | Low    |                 |

| RO        |              | Х           | Х       | Х       | NA     |                 |

| Tempo     |              | Х           |         |         | High   |                 |

**Table 2.1 – Summary of Past Approaches**

### **2.3** Translation and Emulation Efforts

Several research groups have undertaken the task of emulating a program compiled for one ISA in an environment that uses a different ISA. While IBM developed an emulator for executing x86 instructions in a VLIW environment, Transmeta developed a general approach to program translation. Future efforts that provide for compatibility with IA-64 will soon be underway.

### 2.3.1 DAISY

A group at IBM's T.J. Watson Research Center has developed a system that they call DAISY: Dynamically Architected Instruction Set from Yorktown. DAISY focuses on providing complete compatibility between architectures [14].

While most DAISY documentation focuses on VLIW as the target architecture, with modifications DAISY could be used to translate code to execute on processors using the new EPIC instruction set architecture.

As each code fragment is executed for the first time, DAISY translates the fragment into a simple RISC-like intermediate representation. This translation occurs at instruction cache miss time. The translated version of the code is then stored in a caching emulator, which is simply a portion of main memory that is not visible to the old architecture and resembles a cache. Because the translation is cached, the process of translating each fragment must only occur once.

Within DAISY, precise exceptions are handled by scheduling VLIW instructions in the same order as they occurred in the original binary. Unfortunately, this scheduling mechanism will result in code that is far from optimized.

DAISY provides 100% architectural compatibility between ILP architectures and other existing architectures. It also provides fast emulation using clever caching techniques. Such caching techniques would not be necessary, however if the new translated version of the code fragments would actually replace the old code.

### 2.3.2 Crusoe

In January 2000, Transmeta announced the Crusoe package [28]. Comprised as a combination of a low-power VLIW chip and specialized Code Morphing<sup>™</sup> software, Crusoe entered the mobile computing market offering a microprocessor that achieved notable performance while using a fraction of the power.

While the core Crusoe processor is a 4-wide VLIW, it is able to run all legacy x86 code using the Code Morphing<sup>TM</sup> software, which translates x86 instructions into the native instruction set on the fly. The savings in power came from the fact that not all attributes of the x86 architecture needed to be supported in hardware. An entirely new, simple processor could be used.

The Crusoe technology essentially eliminates the ties between the x86 ISA and the underlying hardware. Furthermore, as upgrades to the Crusoe processor are released, the user need only replace the Code Morphing<sup>TM</sup> software, which is specialized to the new processor. Even dramatic changes in the processor will not require any of the software (aside from the code-morphing software) to be recompiled.

The more advanced of the two Crusoe processors introduced in January 2000, can also perform LongRun<sup>™</sup> power management. Unlike many mobile processors which have two clock frequency settings for power savings, full speed or off, the Crusoe processor can dynamically analyze the program(s) being run and adjust the clock frequency to any frequency between maximum and off. Crusoe can also vary the voltage used by the processor as the clock frequency is varied. These adjustments of clock speed and voltage result in cubic reductions in power since power varies linearly with clock speed and quadratically with voltage.

The most ingenious feature of the Crusoe system, is that the Code Morphing<sup>TM</sup> software could be upgraded to not only translate x86 code, but Sparc, Alpha, HP-UX, and IA-64 code as well. This would result in a single system that could transparently execute any legacy code compiled for any architecture without the user knowing or caring about compatibility issues.

The drawback of the Crusoe system is that the translation step is not free; some amount of time must be spent executing the code-morphing software. The translated groups of instructions are maintained in a translation cache, however, amortizing the cost of the translation step. Because the translated code stored in the translation cache is optimized, it can potentially execute faster than the original code.

While the power saving features of the Crusoe processor makes it an competitive option for mobile computing, the translation and optimization features could be employed in the general-purpose (desktop) computing market. The potential for compatibility among all instruction-set architectures is a goal that the entire computing community could certainly benefit from.

#### 2.3.3 FX!32

Compaq (Digital) Corporation introduced a combined emulator and translator that allows x86 applications to run on an Alpha using the Windows NT 4.0 operating system [23]. This system, called FX!32, combines run-time emulation with an off-line optimization system in order to truly distinguish itself from other emulation systems, such as DAISY or Crusoe.

While all of the emulation systems described in this section perform the task of executing non-native instructions on a particular processor, FX!32 employs advanced background dynamic optimization to optimize the Alpha code that is produced during the emulation stage using profiling information gathered at runtime.

The design goals of the background optimization system were user transparency and high performance. To ensure transparency, FX!32 had to be certain that no user interaction was necessary during optimization and that the native code produced was complete and correct. These restrictions resulted in an optimization algorithm that relied on no assumptions or manual interaction of any kind. To ensure the best possible performance, FX!32 leverages many modern advances in compiler optimizations.

A major optimization leveraged by FX!32 is the concept of global optimization. While many other dynamic optimizations are limited to discrete elements such as basic blocks, FX!32 breaks this limitation and is able to perform global optimizations that were currently implemented only during static compile time. This method produces an Alpha executable that performs at least 70% as well as the ideal performance value, which is determined by directly compiling the original source code into an Alpha executable.

### 2.4 **Profiling Monitors For Feedback-Directed Optimization**

An important feature of any dynamic optimization system is its ability leverage profile information about a user to guide runtime optimizations. This allows the software to perform well for the way it is typically used. This concept is known as feedbackdirected optimization. The feedback from the usage patterns guides the optimization process.

The question of *how* to monitor usage statistics for a particular piece of software without hurting software performance is an open research area. The monitoring could be performed in the operating system, such as a daemon that frequently polls the software and gathers statistics much like the monitoring scheme suggested in Thomas Kistler's dynamic run-time optimization system in Section 2.2.4. The problem with a software-monitoring scheme such as this is that it carries a lot of overhead. The scheme requires a system call to be performed at given intervals in order for statistics to be gathered. The

overhead associated with software monitoring may outweigh the benefits gained from dynamic optimization.

Another alternative is to provide dedicated profiling hardware. Since all profiling tasks are performed by the dedicated hardware, there is no performance impact on the running program. The drawback of hardware-based profiling is the expense incurred in adding specialized hardware. Convincing processor manufacturers to dedicate silicon to a task such as profiling may not initially be a welcomed concept. This silicon could be used for a more universal application, such as speeding up the clock or adding a function unit. Furthermore, upgrading the monitoring hardware would require a new processor. Hardware monitoring is much less flexible or upgradeable than its software counterpart.

Several research groups have looked into the problem of program monitoring and profiling. While most groups agree that hardware profiling is the most feasible form of program profiling, their approach and scope differs greatly.

#### 2.4.1 **ProfileMe**

In order to overcome many of the limitations of profiling in the out-of-order processor domain, Digital Equipment Corporation introduced a novel profiling mechanism, called ProfileMe [13]. Rather than employing event counters that monitor specific events such as the number of branch predictions and causing an exception when the counters overflow, the group chose to randomly choose instructions and gather all pertinent information regarding the specific instruction.

The move to instruction sampling arose from problems noted in previous monitors. In order to optimize a program, it is necessary to discern the particular instruction(s) causing an unfavorable event such as a branch misprediction. In previous

36

models, accurate event counts can be maintained, but the method for indicating the instruction causing each event is rarely correct. Out-of-order instruction execution complicated this process, resulting in a nearly random distribution of *causing* instructions. Speculative execution further complicates the process, as speculative instructions were ignored in previous models. ProfileMe permits the analysis of which instructions are aborting and why, while other sampling methods ignore aborted instructions.

ProfileMe is a hardware/software approach to accurately track events and their causes. This is done in two ways. The first method is the *instruction sampling technique*. This technique selects a random instruction and tracks all information about the instruction, such as cache miss rates. Another sampling technique can also be employed. This technique, known as the *paired sampling technique*, collects data about the interaction of other instructions with the random selected instruction.

The major advantages of ProfileMe over techniques such as hardware event counters are:

(1) It collects complete information about each instruction, rather than sampling a small number of events at a time; (2) it accurately attributes events to instructions; (3) it collects information about all instructions, including instructions in uninterruptible sections of code; and (4) it collects information about useful concurrency, thus helping to pinpoint real bottlenecks [13].

The ProfileMe group chose sampling as a means of profiling rather than some of the other methods, such as simulation or instrumentation, for three reasons. First, sampling works on unmodified programs. No additional instructions need to be inserted into the program in order for sampling to proceed. Second, sampling can be used to profile entire systems. Finally, sampling requires very low overhead. The overhead can be directly correlated to the sampling rate. Reducing the sampling interval can therefore directly reduce the overhead caused by sampling.

### 2.4.2 **Profiling for Hot Spots**

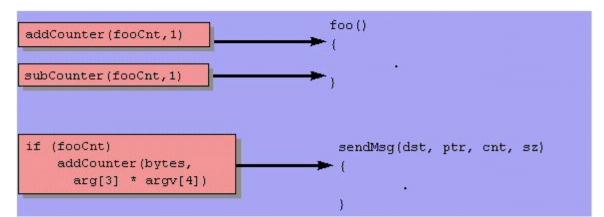

Wen-mei Hwu's group at the University of Illinois extends the typical profiling scheme by also recording the relative importance of the basic blocks encountered [37]. They define a hot spot of code to be a small section of code that is executed very frequently.

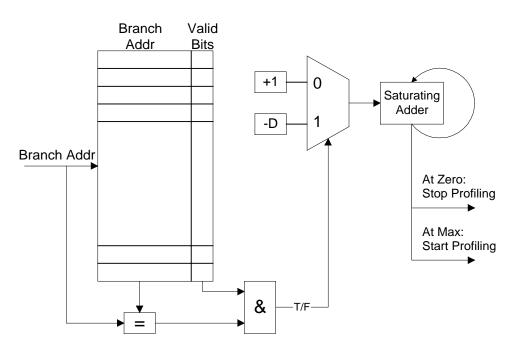

Figure 2.6 – Illinois' Monitor Table Hardware for Hot-Spot Detection [37]

The importance of hot spot determination lies in the realm of dynamic optimization. A frequently executed portion of code that contains a small static footprint, as in the case of hot spots, is a prime candidate for runtime optimization. Due to time restrictions, not all optimizations can be performed at runtime. Therefore potential optimizations must be prioritized. In the case of hot spots, a small amount of time may be required for optimization, compared to the long period of time that will subsequently be spent executing the code. Hot spots should therefore be the top priority for runtime optimizations.

The Illinois group proposes three components to aid in the tasks of hot spot detection and its corresponding dynamic optimization. These components include a *Hot Spot Detector*, a *Monitor Table*, and *Operating System Support*. The hot spot detector can be implemented in hardware to remove overhead. Its main task is to locate the blocks of code that are most frequently executed. The monitor table is a collection of previously identified and optimized hot spots. It is the task of the monitor table to handle the replacement scheme of optimized hot spot code. If it is determined that a particular hot spot is no longer frequently executed, it should be replaced by a better runtimeoptimization candidate. Finally, operating system support is necessary for adding hot spots to the monitor table and gathering blocks into a region that can be passed to the runtime optimizer.

### 2.4.3 The Profile Buffer

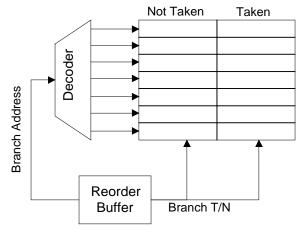

Because of the large overhead that can be encountered during profiling, a group at North Carolina State University proposed a profile buffer for maintaining accurate profile information with low overhead [9].

The profile buffer hardware consists of a decoder and a set of branch counters. Each row in the buffer has two buffer entries associated with it, one is a counter that maintains the number of times the branch was taken, the other maintains the number of times the branch was not taken.

Figure 2.7 – The Profile Buffer Hardware [9]

As a branch is encountered, it is converted to an index into the buffer table. Once the outcome of the branch is known, the corresponding entry in the buffer table is updated. After a certain amount of time and before the profile buffer fills, the contents are spilled to memory. In order to hide the latency of the buffer spill, the action is performed during a context switch.

Due to the fact that the profile buffer restricts profiling to include only branch outcomes, it alone is not useful in the context of dynamic optimization. Dynamic optimization requires a great deal more profile information in order to perform any worthwhile optimizations. If the profile buffer was included in a large set of monitoring hardware, however, its low-overhead scheme could be very useful to runtime optimization where performance is the top priority.

### 2.4.4 Itanium Monitors

Chapter 4 and Chapter 5 of this thesis focus on dynamic optimization in the realm of EPIC architectures. For this reason, the particular monitoring features that will be available in the first chips employing the IA-64 architecture are of particular interest.

40

Zahir, et al. of Intel Corporation recently wrote of the specific features that will be incorporated into the Itanium processor line that will radically simplify the task of monitoring and profiling executing programs [45]. The new features focus on locating performance bottlenecks.